AFFELAのE&Eアーキテクチャに込めた、未来への準備

E&Eアーキテクチャとは、自動車に搭載された ECUやセンサーなどのデバイスを繋ぐシステムの設計・構造を指す。OTAによる継続的なソフトウェア更新を前提としたSDVの発展、それにともなう車両機能の高度化や増加の一途をたどるECUの接続・制御の複雑化から、E&Eの進歩はより重要になっている。

そうしたなかでソニー・ホンダモビリティ(以下、SHM)が志向するのは、未来の体験に備えるための、ハードウェアの制限を取り払うE&Eだ。先進的なアーキテクチャに加え、高度なスペックのSoCを搭載していることが特徴となる。

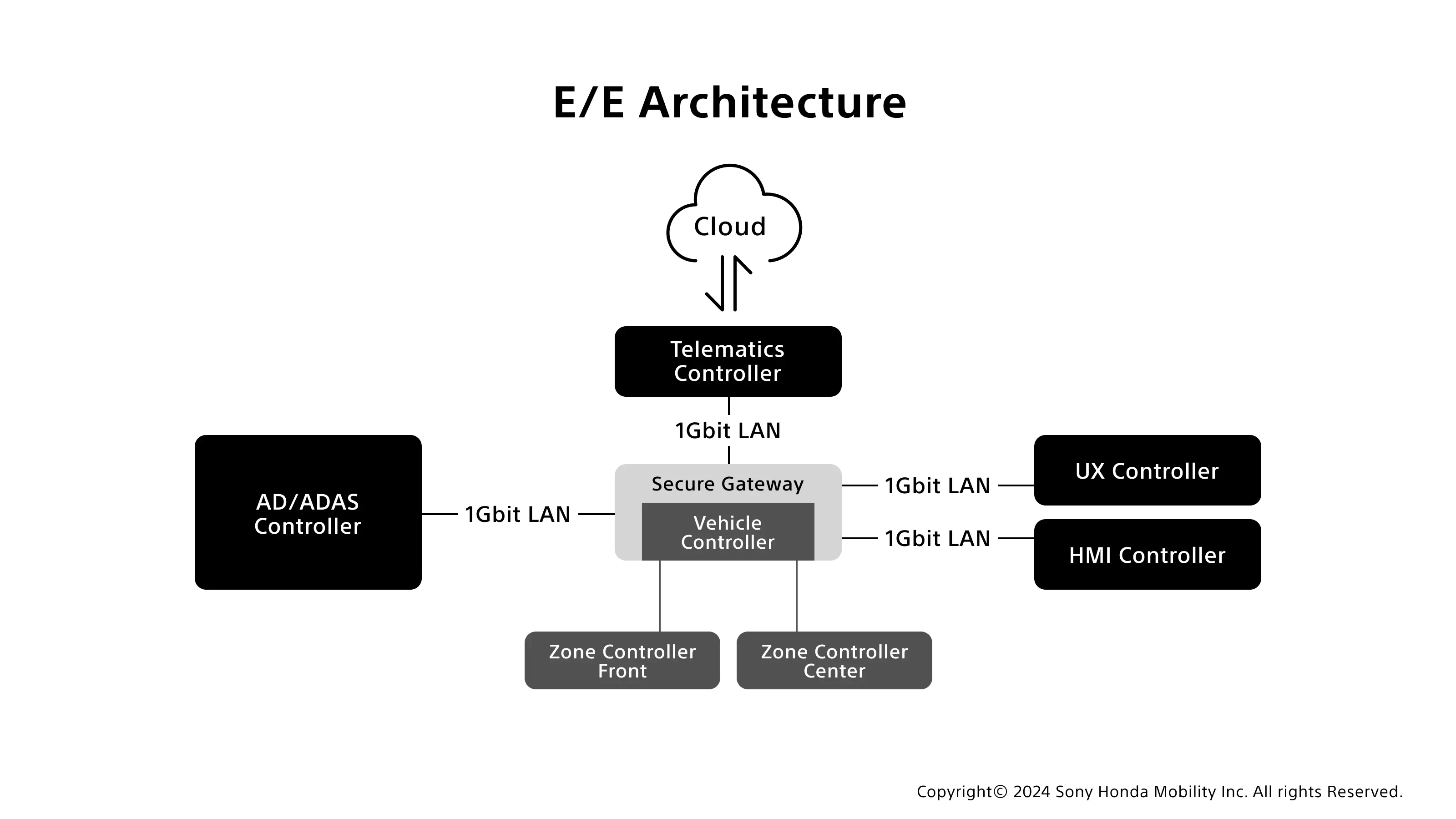

AFEELAが採用するE&Eアーキテクチャ

次世代のE&Eアーキテクチャは、各機能を制御するソフトウェアを1つのECUに統合・集約することで、システムや車両の構造を簡素化する方向へと向かっている。機能改善時にECUごとに改修を加えることなく、集約した一つのECUをアップデートすればクルマの振る舞いを変えられること、ECUとデバイスを繋ぐ物理的なハーネスを削減できることなどがその背景にある。

E&Eのアーキテクチャには大きくドメイン/ゾーン/セントラルアーキテクチャの考え方があるが、現在のSDVのアーキテクチャはドメインアーキテクチャからゾーンアーキテクチャへと移行している。

SDV業界を牽引するテスラが完全な中央集権型のセントラルアーキテクチャを採用している一方で、既存OEMによる次世代SDVのE&Eアーキテクチャは、今後ゾーン+セントラルアーキテクチャが主流となっていくことが見込まれる。AFEELAにおいては、それらのアーキテクチャを含め、最適解を検討中だ。

未来の体験に備える、SHMの意思

こうしたアーキテクチャをベースに、SHMの意思は特にIVI、AD/ADASの2つの領域に宿っている。各領域に、1個だけでなく複数のSoCを配置(IVIには2個、ADには5個)。 すべてにQualcomm Technologies社のSoC「Snapdragon® Digital Chassis™」を採用した。同SoCの演算性能は、最大800TOPSと他OEMが採用しているものと比べても抜きん出ており、現代最高峰のスペックを誇る。

なぜそのような「高度なスペック」が必要なのか。それは、SoCの処理能力といったハードウェア側の制約によって、ソフトウェア更新による機能改善に限界が生じるリスクを、極力排除した設計にしていくことが今後のE&Eにおいては非常に重要になるからである。将来的な自動運転の普及もふくめ、OTAでのソフトウェア更新によるクルマの性能向上を継続的に行うにあたっては、CPUの処理能力(ハードウェア)の限界はアップデートの頭打ちに繋がってしまう。パソコンやスマートフォンがわかりやすいが、技術の進歩は早く、その限界は必ず訪れる。しかし、こうしたハードウェアの限界をできる限り取り払うことも同時に求められていくのだ。

“クルマを超えた体験”のための未来思考を

AFEELA、そしてSHMは、クルマを超えた体験をユーザーに届けていくこと、クルマを介した共創プラットフォームを提供していくことを目指している。クリエイターたちがそこで表現する体験、SDVが拡張するクルマの新しい未来に備え、ハードウェアの構えを強固にしておく。そのために、いま考えられる限りの高度なスペックの頭脳を採用することが、次世代E&EにおけるSHMの意思である。

とはいえ、先述のハードウェアの構造やスペックの制限は、今後のSDV、E&Eの大きな課題のひとつである。ハードウェアの限界が来たときの事を考えた、可能な限りクラウド側に実装し、エッジ側(車両側)の演算負荷を低減させ、クルマが継続的に進化する事ができるE&Eアーキテクチャが理想的な姿だ。そうした、さらなる未来を想像していくことも、SHMのアイデンティティに組み込まれている。

Interviewer: Takuya Wada

Writer: Asuka Kawanabe

Related